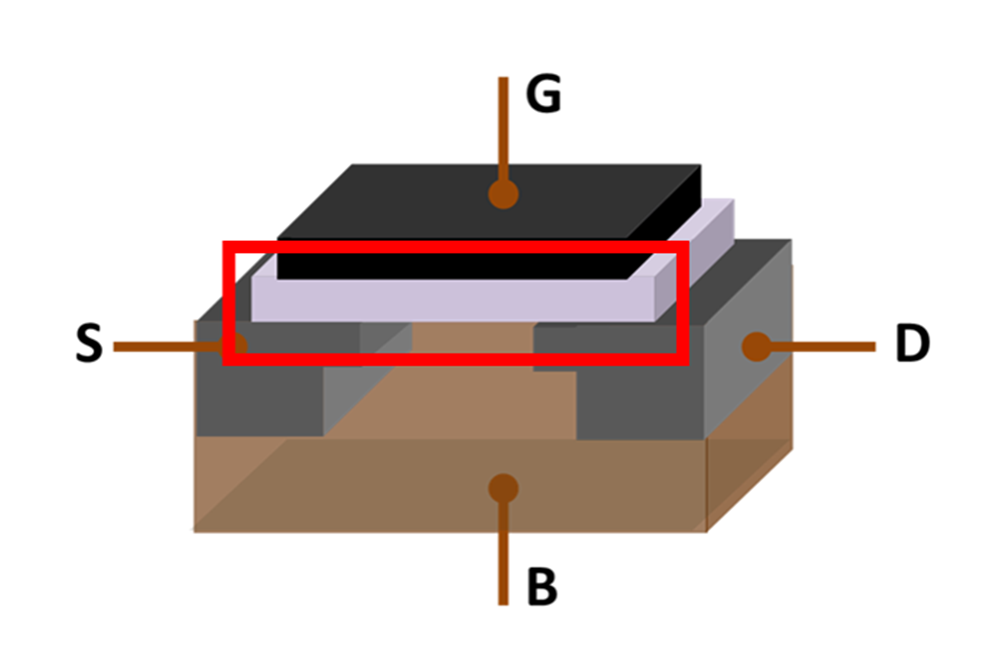

半導体チップと言われれば一般的にMOSFE構造のモデルを指す場合が多いです。

MOSFETとは、電界効果トランジスタ(FET)に金属酸化膜半導体(MOS)を組み合わせた言葉で、入力電圧から生じる電界を用いてスイッチ動作を行うトランジスタの一種です。

電界効果トランジスタ (MOSFET) のプレーナ構造により、ウエハ上に複数のMOSFETを製造することができ、一枚の半導体チップで多くの信号を入出力することが可能になります。

また、第1世代のバイポーラ接合トランジスタ(BJT)とは異なり、MOSFET ははんだ付けプロセスを必要としません。

今回は、具体的なMOSFETの製造工程を詳しく見ていきましょう。

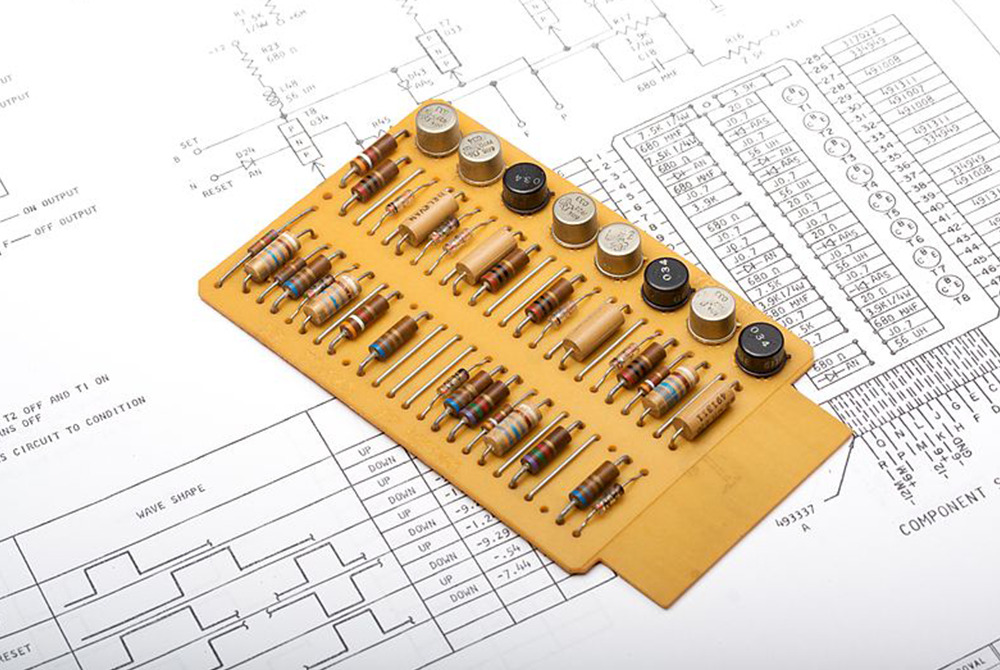

身の回りの電子製品を分解してみると、その基本的な構造は、トランジスタ、乾電池、バッテリー、インダクタなどの各種ユニット電子部品をプリント基板(PCB)上に固定することによって電化製品のコントロールをしています。

- ¹BJT:バイポーラ接合トランジスタは、半導体内のP型半導体とN型半導体を特定のプロセスで組み合わせた(PN組み合わせ)トランジスタ。

- ²PCB:プリント基板(Printed Circuit Board)、ほとんどの電子製品に使用される半導体基板で、基板上に回路が配置され、その表面にさまざまな電子部品が溶接されています。

このトランジスタのような構造を、半導体ウエハ上に作成することを『MOSFET構造』と呼びます。

それでは一番オーソドックスな半導体素子であるMOSFETの製造工程をご紹介していきます!

MOSFETの製造プロセスとは?

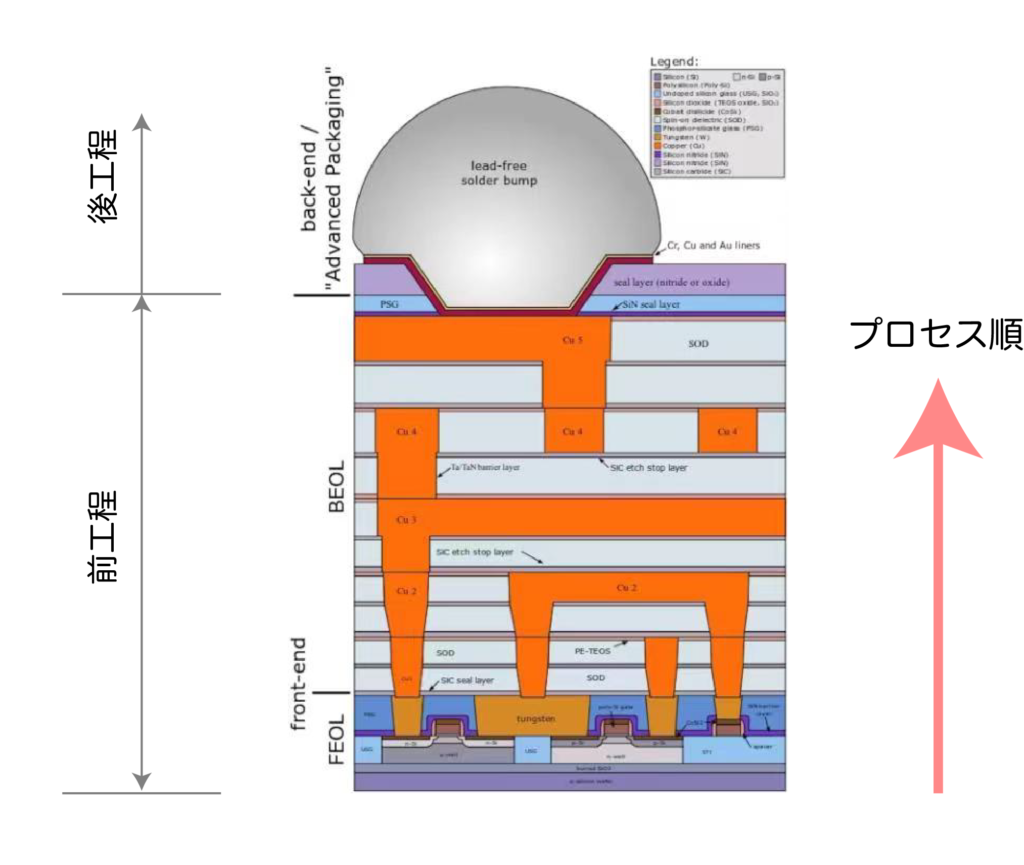

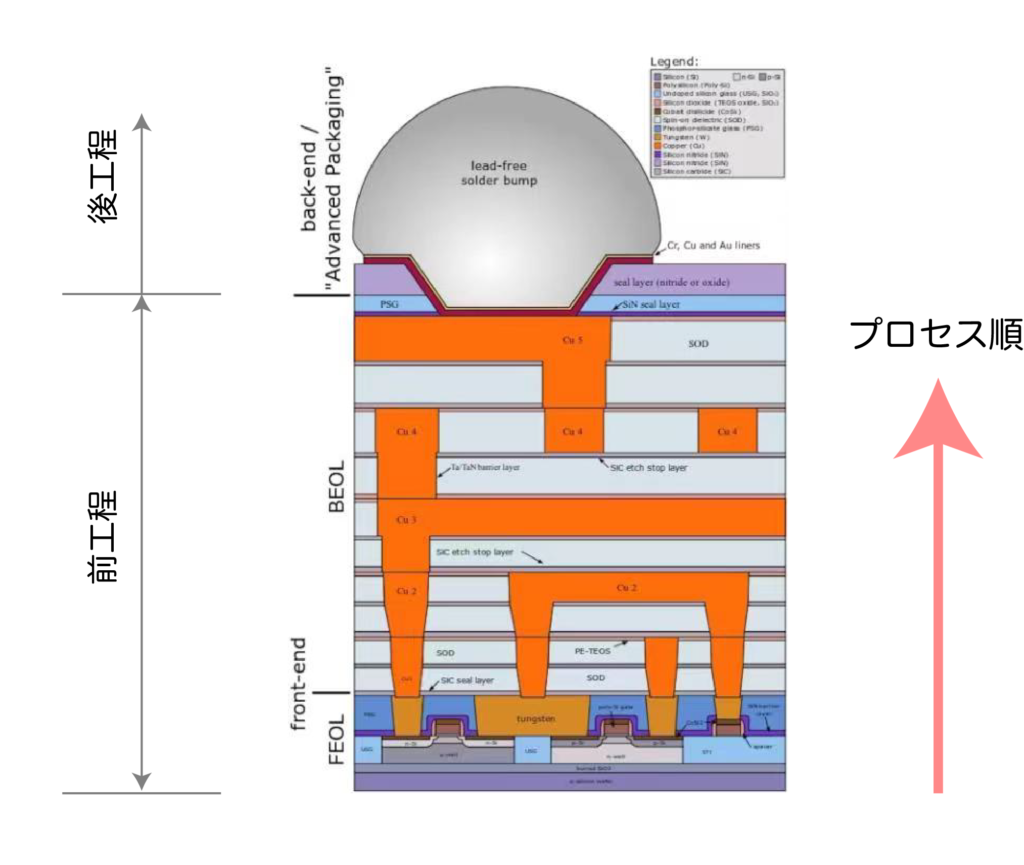

半導体プロセスは大きく分けて前工程と後工程に分けられています。

また前工程も『フロントエンド(FEOL、Front End Of the Line)』と呼ばれるシリコンウエハにトランジスタ層を形成するまでの工程と、『バックエンド(BEOL、Back End Of the Line)』の多層配線層を形成するまでの工程に分けることができます。

- 前工程:シリコンウエハにパターン回路を形成まで

- 後工程:回路が形成されたシリコンウエハを半導体チップに切り出して、出荷するまで

FEOL段階でMOSFET構造が形成され、その後溶接プロセスの代わりに金属配線が使用され、さまざまな電子部品が接続されます。

このような半導体素子を利用した半導体チップは、微量の電気を流すことでONとOFFを判別し、入力と出力をスイッチすることが出来ます。

半導体素子の母材となるシリコンウエハは『真性半導体』であり、電気の伝導率はほとんどありません。

そこで電気を通すための様々なプロセスを経て、1つのチップに数十億個のトランジスタを形成する秘密があります。

半導体素子に電気を流すようにするプロセスについては、こちらを参考にしてください!

主にドーパントと金属膜を形成するCVDやPVDという方法があります。

半導体チップの前工程とは?

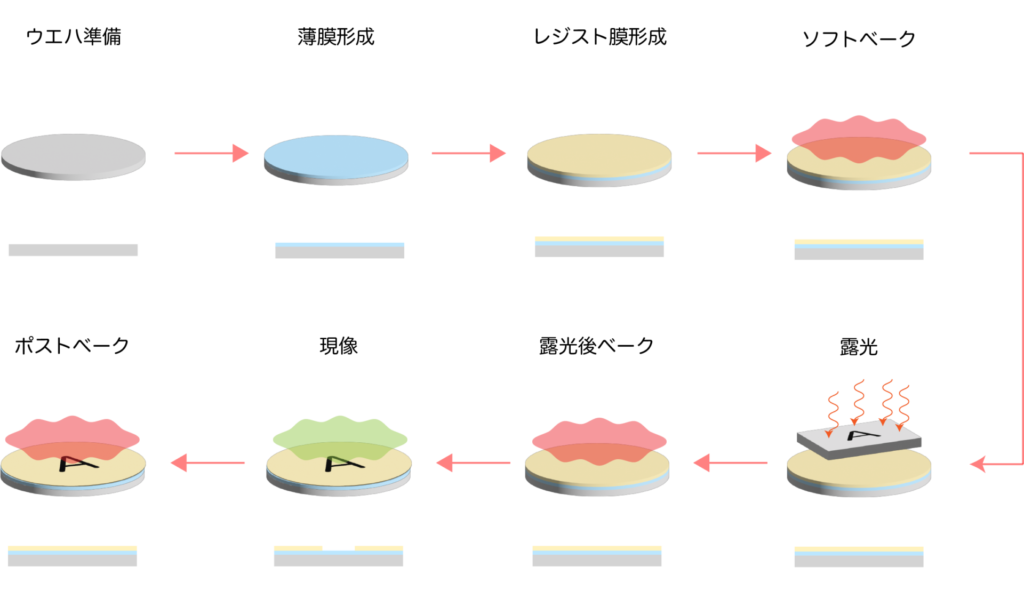

半導体チップを製造する前工程として、主には以上のプロセスがあります。

ウエハの酸化膜形成、フォトリソグラフィー、エッチングなどは前工程であり、FEOLとBEOLに含まれています。

それぞれの半導体チップによってプロセスの目的が異なり、特定の装置を使用する頻度や回数も異なりますが、基本的な目的は、多数の微細なレジストパターンを形成することです。

一般的に言えば、半導体製造の8大主要プロセスは以下の通りです。

- ウエハ製造

- 酸化膜形成

- フォトリソグラフィ

- エッチング

- 蒸着

- 金属配線

- 検査

- パッケージング

ただし、これら8つの工程を1つの工場で完了させることはできません。

つまりウエハを作る工場があり、前工程をする工場、後工程をする工場などに一般的には分けられています。

8大プロセスの詳しい内容については、こちらを参考にしてください!

酸化膜の形成プロセス

酸化膜形成の目的

半導体製造プロセスは、ウエハの製造から始まり、下から上へ進みます。

この工程は、レンガを積み上げるように何十層も重なっていきますが、ただ均一な材料を積み上げていくだけではありません。

半導体チップ層で、形状の異なる材料を均一な材料にするには、不要な部分を切り落としたり、必要な部分を特定の物質でコーティングしたりするなど、複数の工程が必要です。

酸化膜の形成プロセスの目的は、シリコンウエハ(Si)と酸素(O2)を反応させることによって、シリコン上に絶縁膜を形成して電流の漏電やショートを防止することです。

私たちの日常生活の中でも、ガラスは化学的安定性が高く、各種飲料や塩酸、硫酸などの薬品の容器としてよく使われていることがわかります。

半導体製造プロセスにおいては、酸化プロセスにより形成される酸化膜も安定した化学性質を持っています。

他の物質の侵入を防ぐことができるため、イオン注入工程において非常に実用的です。

酸化膜は、回路間の電流の流れを防ぐためにも使用されています。

MOSFET 構造の中核はゲートになっており、MOSFETは、ゲートが電流チャネル (SとDの中間部分) に直接接触しておらず、「間接的に」のみ機能するという点で、 BJTトランジスタとは異なります。

MOSFETが動作していないときの消費電力が小さいのもこのためです。

MOSFETはゲート電極と電流チャネルを酸化膜で絶縁しており、この酸化膜をゲート酸化層(Gate Oxide)と呼びます。

最近量産されている最先端の半導体製品は徐々に微細化しており、酸化膜の代わりにHKMG4などのさまざまなゲート絶縁層が使用されるようになります。

- イオン注入:半導体製造プロセスでは、純粋なウェーハを半導体状態に変えるために、III 族または V 族元素を特定の方法で半導体基板の指定された領域に組み込みます。

- 4HKMG (High-K メタルゲート):漏れ電流を効果的に低減できる新世代の MOSFET ゲートです。従来のポリシリコンゲートの代わりに金属を使用し、酸化シリコン絶縁膜の代わりに高誘電体 (High-K) を使用します。

保護膜として使用できる物質は二酸化ケイ素(SiO2)だけではありません。

蒸着(CVD/PVD)による保護膜で覆ったり、既に形成されている回路の一部を保護として利用することも可能です。

酸化プロセスはウエハ材料の構造を利用し、ウエハ中の多数のシリコン原子を酸化して保護膜を形成します。

PVDプロセスについて詳しくは、こちらを参考にしてください!

酸化膜の形成プロセスの種類

酸化プロセスは以下の通り 3 つのカテゴリに分類できます。

- ウェットプロセスで酸化膜の形成

- ドライプロセスで酸化膜の形成

- ラジカルプロセスで酸化膜の形成

それでは1つ1つ詳しくプロセス内容について説明していきます。

ウェットプロセスで酸化膜の形成

ウェット酸化は、ウエハと高温の水蒸気(水)を反応させて酸化膜を生成するもので、化学式は次のようになります。

ウェット酸化では、酸化膜は急速に成長しますが、酸化膜全体の均一性と密度は低くなります。

またウエハと溶液の反応中に、水素などの副生成物も生成しますので、 ウェットでの酸化プロセスは制御が難しい性質があるため、この方法は半導体の性能にとって重要なコア領域には使用できません。

ドライプロセスで酸化膜の形成

ドライ酸化では、高温の酸素を使用してウエハと直接反応します。

酸素分子は水分子より重く (32 vs 18)^5であるため、比較的ゆっくりとウエハの内部に浸透します。

ドライ酸化はウェット酸化に比べて酸化膜の成長速度が遅くなるため、コントロールしやすいという特徴があります。

またドライ酸化は、化学反応後の副生成物(H2)が発生せず、酸化膜の均一性や緻密性が高いという利点があります。

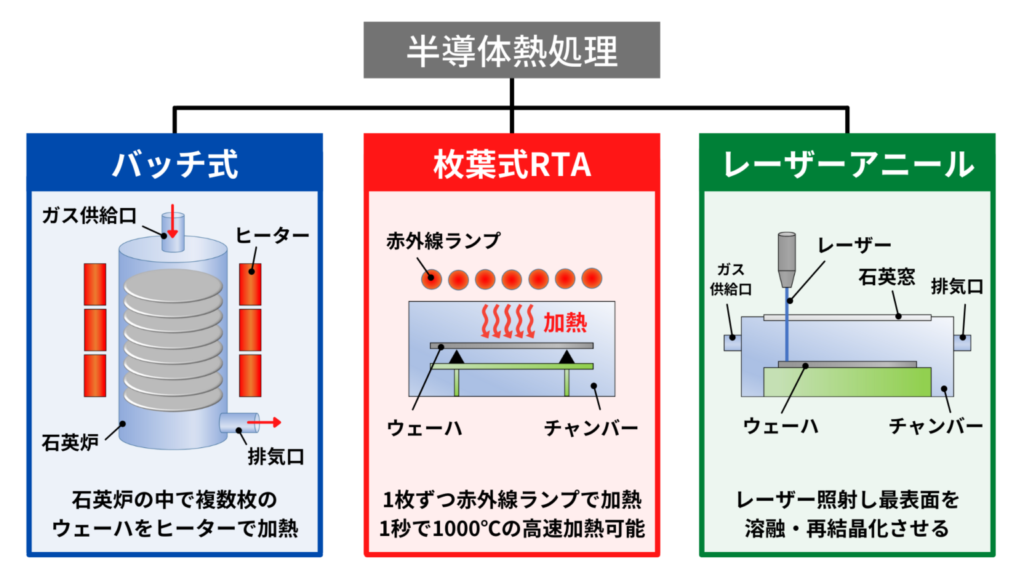

このドライ酸化は、一般的にアニールのことを指しているます。

アニールに関してはこちらで紹介していますので、参考にしてください!

フリーラジカルプロセスで酸化膜の形成

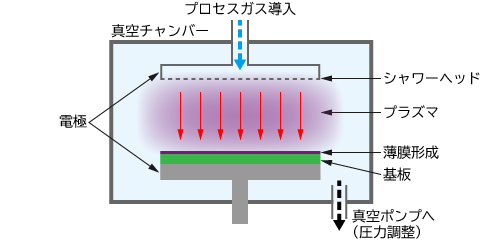

出典:松定プレシジョン(https://www.matsusada.co.jp/column/sc_prasma.html)

フリーラジカル酸化は、ウェット酸化とドライ酸化の2つとは異なるプロセスです。

ウェット酸化とドライ酸化は両方とも、温度を上昇させることで天然ガスのエネルギーを増加させ、それによってガスとウエハ表面の間の反応を促進します。

しかしフリーラジカル酸化では、ウエハを酸化させる際に、高周波やマイクロ波を用いて発生させた酸素プラズマを用いることで酸化膜を形成します。

つまり、酸素原子と水素分子が高温条件下で混合されて、化学反応性の高いフリーラジカルガスが形成され、その後フリーラジカルガスがウエハと反応します。

フリーラジカルの化学活性は非常に強いため、フリーラジカル酸化反応が不完全になる可能性は極めて低いです。

したがって、このフリーラジカル酸化の方法はドライ酸化よりも良好な酸化膜を形成することができる。

ドライ熱やウェット酸化に比べて、低温での酸化が可能なため、シリコンウエハ中の積層欠陥や転移の発生の抑制、不純物の再分布の減少とメリットがあります。

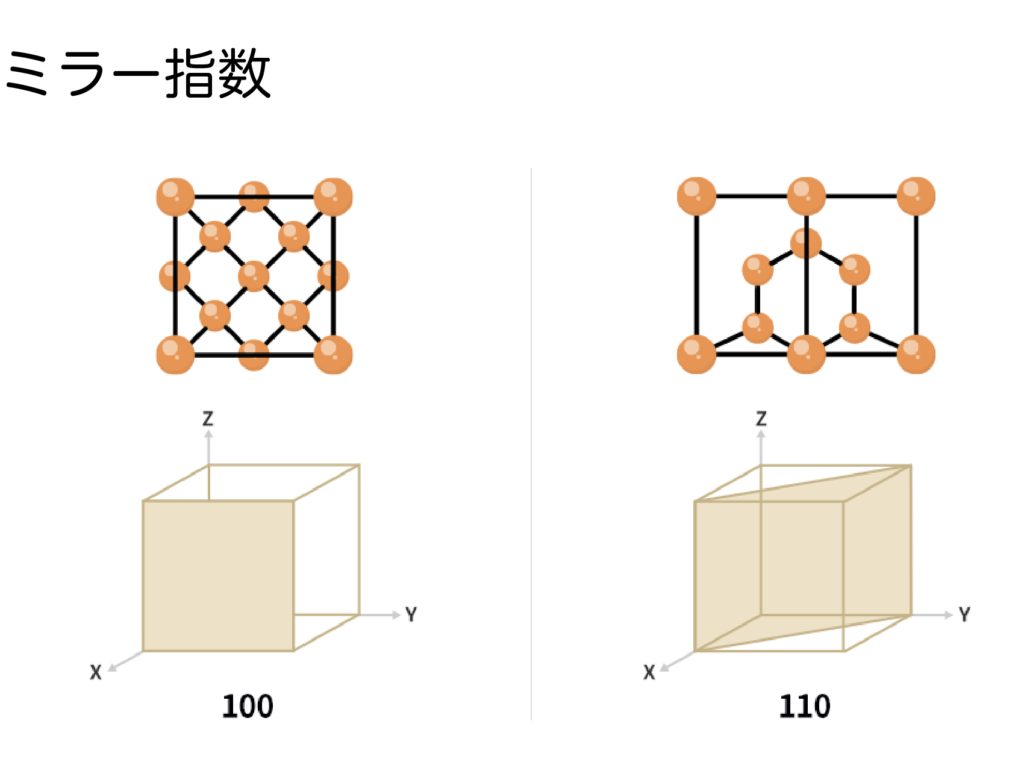

また半導体の製造プロセスでは、あらかじめ生産するウエハの結晶化方向が、同じ単結晶ウエハを使用します。

100と110の数字はシリコンの結晶化方向を表し、ウェット酸化とドライ酸化では、ウェーハの上面(100)方向の酸化膜の成長速度が相対的に遅く、側面(110)方向の酸化速度が速いという特徴があります。

100 方向のシリコン原子はより密に配置されているため、ドライ酸化またはウェット酸化では酸化性ガスが結晶に侵入してシリコンと反応しにくく、フリーラジカル酸化はこの点で比較的容易です。

またフリーラジカル酸化により、酸化膜が形成されにくい角丸部分にも均一な酸化膜を形成することができ、反応性の弱い、窒化膜シリコン(Si3N4)でもシリコン原子を「捕捉」して酸化反応を起こすことができます。

半導体の微細化の難しさが増すにつれ、このようなフリーラジカルを利用した三次元構造での酸化膜の形成プロセスを導入し始めています。

したがって均一な厚さの高品質な保護膜を製造することが、ますます重要になっており、酸化プロセスもより重要になっています。

- 窒化ケイ素(Si₃N₄):窒化ケイ素は、半導体電子部品の製造プロセス中に電子表面を覆うために堆積される保護膜の一種です。

酸化膜の形成装置

出典:Semi journal(https://semi-journal.jp/basics/process/anneal.html)

ガス注入口から酸化装置内に流入した反応性ガスは加熱され、ウエハと酸化反応を起こします。

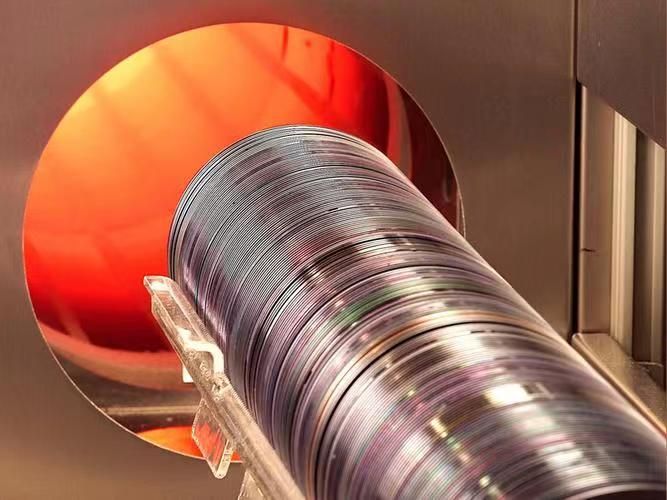

先にガスにさらされる部分と、後でガスにさらされる部分の酸化度の差を小さくするために、ウエハにダミーウェーハを使用し、均一性を調整します。

またプロセスでは数十枚のウエハを同時に配置して酸化形成する装置もあり、酸化速度が非常に速いことがわかります。

アニールによる酸化膜の形成については、こちらを参考にしてください!